SPI 接口简介

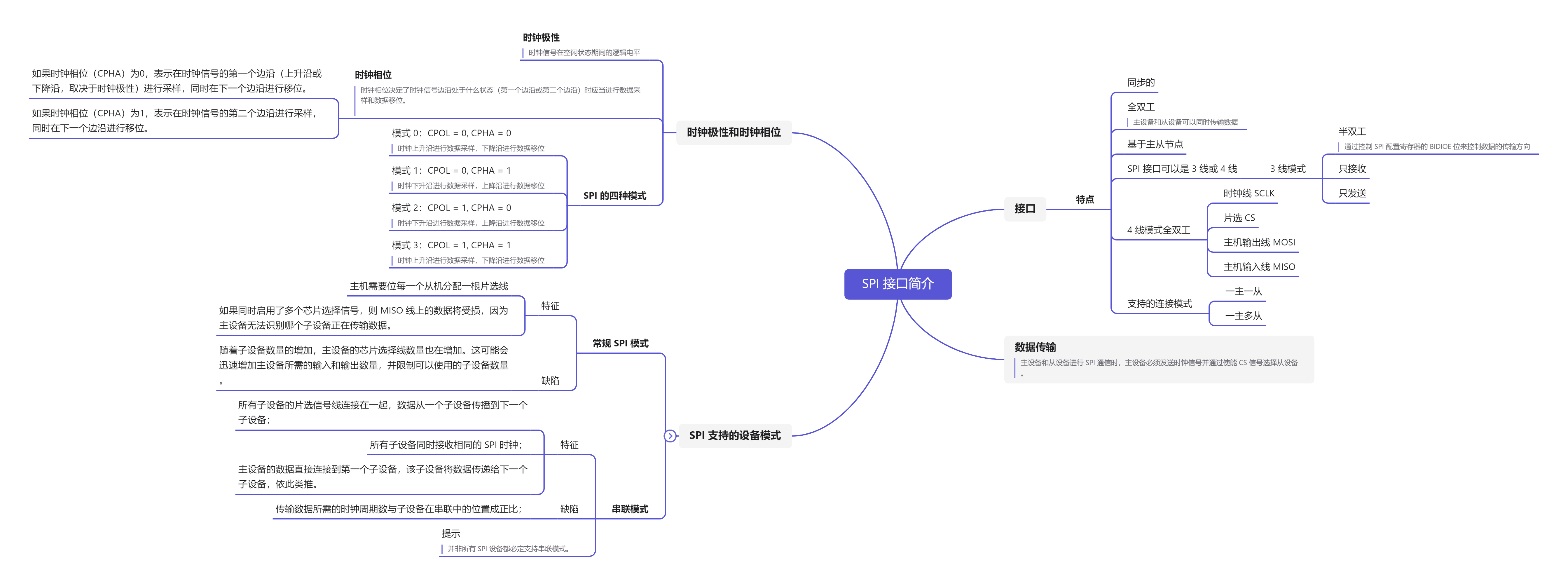

思维导图

串行外围接口(SPI)是微控制器与传感器、ADC、DAC、移位寄存器、SRAM等外围集成电路之间最广泛使用的接口之一。本文简要介绍了 SPI 接口,然后介绍了模拟器件的支持 SPI 的开关和多路复用器,以及它们如何帮助减少系统板设计中的数字 GPIO 数量。

SPI 是一种同步的、全双工的、基于主节点-从节点的接口。主节点或从节点的数据在上升或下降的时钟沿同步。主节点和从节点都可以同时传输数据。SPI 接口可以是 3 线或 4 线。本文重点介绍流行的 4 线 SPI 接口。

接口

4 线 SPI 设备有四根信号线:

时钟线(SPI CLK, SCLK)

- 生成时钟信号的设备称为主机。主设备生成的时钟信号用来确保主设备和从节点之间传输的数据是同步的。与 I2C 接口相比,SPI 设备支持更高的时钟频率。用户应查阅产品数据表以获取 SPI 接口时钟频率规格。

片选线()

- 主机的片选信号线用于选择从机。一般情况下,片选线保持高电平。主机与从机通信时会拉低对应从机设备的片选线(保持低电平),通讯完成后拉高片选线断开连接。本文中选择从机设备时,片选信号线始终是低电平;

- 当有从模式设备时,主设备需要为每个从设备分配一个片选信号线了;

- 片选分为硬件片选和软件片选:

- 通常使用软件片选:将主机的 GPIO 配置为输出模式,电平状态初始化为高电平,片选的电平状态需要由用户去控制。

- 硬件片选:有些主机的 SPI 支持硬件片选,片选的电平状态不需要用户去控制,具体使用方法请查看所使用的主机数据手册。

主机输出(从机输入)线(MOSI)

- 数据传输线。MOSI 数据传输方向是主机到从机。

主机输入(从机输出)线(MISO)

- 数据传输线。MISO 数据传输方向是从机到主机。

SPI 接口只能有一个主设备,但是可以有多个从设备,支持的模式有:

- 一主一从;

- 一主多从。

图1. 展示了 SPI 主从设备的接法。

数据传输

主设备和从设备进行 SPI 通信时,主设备必须发送时钟信号并通过使能 CS 信号选择从设备。通常,片选线是一个低电平有效的信号;因此,主设备必须在该信号上发送逻辑 0 以选择从设备。SPI 是一个全双工接口;主设备和从设备可以通过 MOSI 和 MISO 线同时发送数据。在 SPI 通信期间,数据的传输(以串行方式移位到 MOSI/SDO 总线上)和接收(在总线上采样或读取数据(MISO/SDI 上的数据))可以同时进行。串行时钟边缘同步数据的移位和采样。SPI 接口允许用户灵活选择时钟的上升沿或下降沿来采样和移位数据。请参阅设备数据表以确定使用 SPI 接口传输的数据位数。

时钟极性和时钟相位

在 SPI 中,主机可以选择时钟的极性和相位。主机设备通过设置其 SPI 配置寄存器中的 CPOL 位来设置时钟信号在空闲状态期间的极性。空闲状态指的是片选线的电平变化这段时间:

- 传输开始时,片选线由高电平转变为低电平;

- 传输结束时,片选线由低电平转变为高电平。

主机设备通过设置其 SPI 配置寄存器中的 CPHA 位来设置时钟信号的相位。时钟相位决定了时钟信号边沿处于什么状态(第一个边沿或第二个边沿)时应当进行数据采样和数据移位。

- 如果时钟相位(CPHA)为0,表示在时钟信号的第一个边沿(上升沿或下降沿,取决于时钟极性)进行采样,同时在下一个边沿进行移位。这意味着数据在每个时钟周期的开始时被采样,然后在时钟周期的末尾被移位。

- 如果时钟相位(CPHA)为1,表示在时钟信号的第二个边沿进行采样,同时在下一个边沿进行移位。这意味着数据在每个时钟周期的末尾被采样,然后在下一个时钟周期的开始被移位。

移位(Shift)是指将数据从一个位置传送到另一个位置的过程,在这里指的是在 MISO 和 MOSI 上传输数据位。

主设备必须根据从设备的要求选择时钟极性和时钟相位。根据 CPOL 和 CPHA 位的选择,有四种 SPI 模式可用。表 1 显示了这四种 SPI 模式。

| SPI 模式 | 时钟极性 | 时钟相位 | 空闲状态时,时钟的极性 | 时钟相位对数据采样和移位的影响 |

|---|---|---|---|---|

| 0 | 0 | 0 | 逻辑低电平 | 在时钟信号的上升沿进行采样,在下降沿移位数据。 |

| 1 | 1 | 0 | 逻辑低电平 | 在时钟信号的下降沿进行采样,在上升沿移位数据。 |

| 2 | 1 | 0 | 逻辑高电平 | 在时钟信号的下降沿进行采样,在上升沿移位数据。 |

| 3 | 1 | 1 | 逻辑高电平 | 在时钟信号的上升沿进行采样,在下降沿移位数据。 |

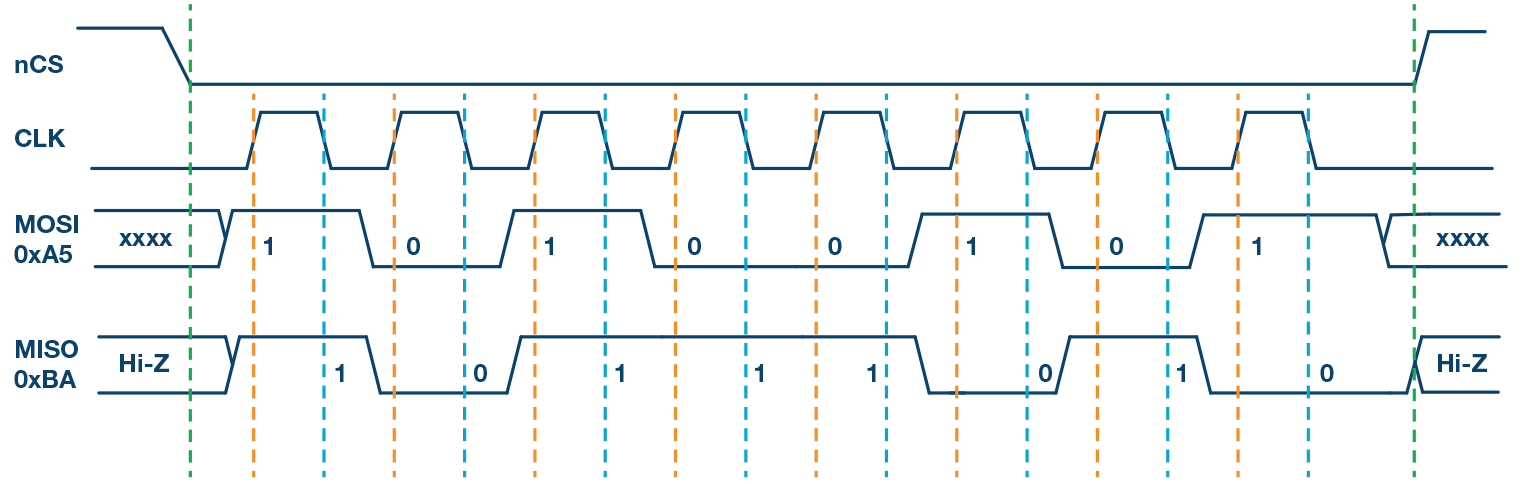

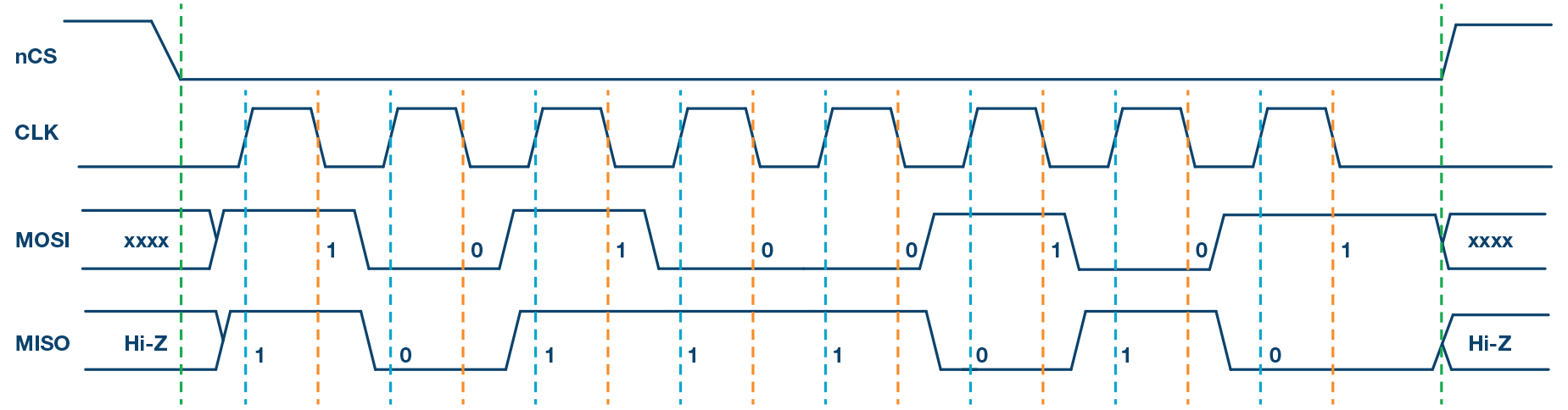

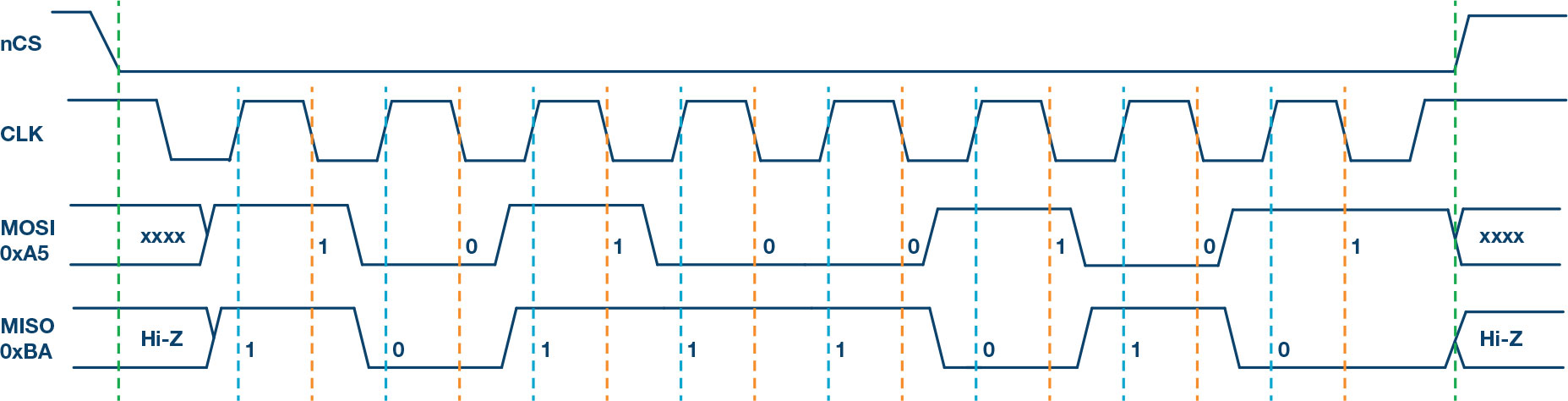

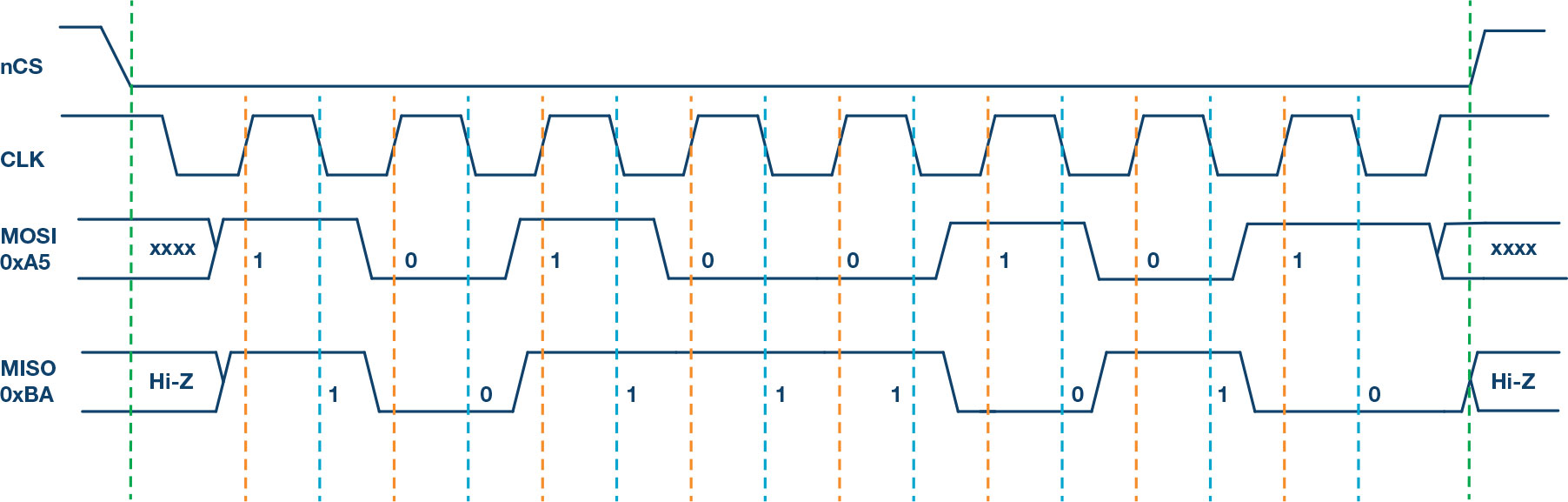

图 2 到 图 5 展示了在四种 SPI 模式下的通信示例。在这些示例中,数据显示在 MOSI 和 MISO 线上。传输的开始和结束由虚线绿线表示,采样边缘由橙色表示,移位边缘由蓝色表示。请注意,这些图表仅用于说明目的。

图 2 显示了 SPI 模式 0 的时序图。在此模式中,时钟极性为 0,表示时钟信号的空闲状态为低电平。在此模式中,时钟相位为 0,表示数据在时钟信号的上升沿上采样(由橙色虚线表示),数据在时钟信号的下降沿上移位(由虚线蓝线表示)。

图 3 显示了 SPI 模式 1 的时序图。在此模式中,时钟极性为 0,表示时钟信号的空闲状态为低电平。在此模式中,时钟相位为 1,表示数据在时钟信号的下降沿上采样(由橙色虚线表示),数据在时钟信号的上升沿上移位(由虚线蓝线表示)。

图 4 显示了 SPI 模式 2 的时序图。在此模式中,时钟极性为 1,表示时钟信号的空闲状态为高电平。在此模式中,时钟相位为 0,表示数据在时钟信号的下降沿上采样(由橙色虚线表示),数据在时钟信号的上升沿上移位(由虚线蓝线表示)。

图 5 显示了 SPI 模式 3 的时序图。在此模式中,时钟极性为 1,表示时钟信号的空闲状态为高电平。在此模式中,时钟相位为 1,表示数据在时钟信号的上升沿上采样(由橙色虚线表示),数据在时钟信号的下降沿上移位(由虚线蓝线表示)。

一主多从模式配置

单个 SPI 主设备可以连接多个子设备。连接模式有常规模式和串联模式连接。

常规 SPI 模式

在常规模式下,主设备需要为每个子设备提供一个独立的芯片选择信号。一旦主设备启用芯片选择信号(拉低),MOSI/MISO 线上的时钟和数据就可用于所选子设备。如果同时启用了多个芯片选择信号,则 MISO 线上的数据将受损,因为主设备无法识别哪个子设备正在传输数据。

如图 6 所示,随着子设备数量的增加,主设备的芯片选择线数量也在增加。这可能会迅速增加主设备所需的输入和输出数量,并限制可以使用的子设备数量。有多种技术可用于在常规模式下增加子设备的数量,例如使用复用器生成芯片选择信号。

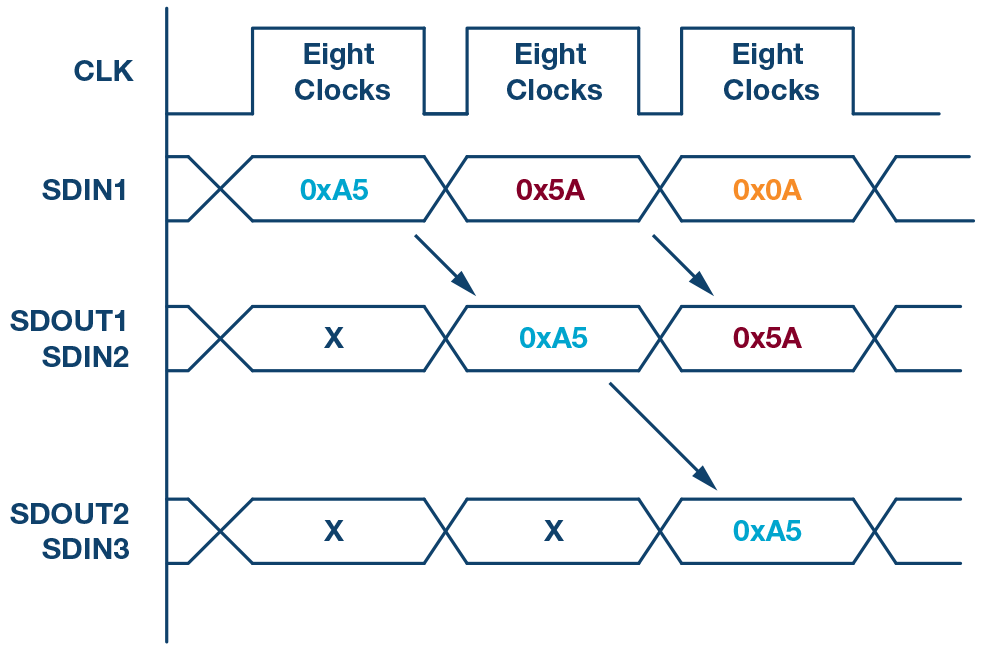

串联模式

在串联模式下,子设备的配置使得所有子设备的片选信号线连接在一起,数据从一个子设备传播到下一个子设备。在此配置中,所有子设备同时接收相同的 SPI 时钟。主设备的数据直接连接到第一个子设备,该子设备将数据传递给下一个子设备,依此类推。

在此方法中,随着数据从一个子设备传播到下一个子设备,传输数据所需的时钟周期数与子设备在串联中的位置成正比。例如,在图 7 中,在一个 8 位系统中,需要 24 个时钟脉冲才能在第三个子设备上可用数据,而在常规 SPI 模式下只需要八个时钟脉冲。图 8 显示了时钟周期和数据在串联中传播的情况。并非所有 SPI 设备都必定支持串联模式。请参考产品数据表以确认是否支持串联。

参考文献

[1] Piyu Dhaker. "Introduction to SPI Interface." Analog Devices, Inc., SEP 2018.